### The most imaginative g 01-660 7231 24 HOUR CREDIT CARD ORDERING

PAINTBOX is a must for every 48K SPECTRUM owner! If you want to exploit the full graphics capability of your machine you can do so ... simply and

easily with PAINTBOX Take a look at the screen prints shown above. They are the sort of thing you could produce on your SPECTRUM. PAINTBOX gives you an entire suite of graphics programming gids in one

#### integrated program. For instance: **UDG EDITOR**

The facility to define and re-define up to 84 graphics characters for your programs or for use in screen-planning

UDG DRAWING BOARD A fully-integrated UDG planner for defining up to 4 Banks of characters Planning facilities include MIRROR, INVERSE, ROTATE, FILE.

SKETCHPAD An experimentation "window" for developing the UDG set

#### PRECISION PLOTTER

An amazingly versatile high resolution drawing board which includes PAPER choice INK choice PLOT, DRAW, CIRCLE, FILL, ARC, OVER, ERASE, and STORE!

#### SCREEN PLANNER

Combining PRECISION PLOTTER and UDG characters! A multi-purpose graphics facility to enable you to produce incredible screen graphics. All work can be sent to a Printer and SAVED as SCREEN or as CODE with its own built-in machine code routine for instant recall from BASIC

The program comes with a DEMO program and a 28 page book that's packed with hints and tips on how to get the best from PAINTBOX.

PAINTBOX is ideally suited for use with the Print 'n' Plotter Spectrum Jotter Package – the first and best graphics planning pad for the Spectrum! So why not place an order today? Write, call, or see your local dealer.

Post to: Dept S Print 'n' Plotter Products Ltd. 19 Borough High Street, London SEI 9SE Please send me:

"PAINTBOX" SOFTWARE @ £7.50 (+75p p+p SPECTRUM JOTTER PADS @ \$7.50 (\$1.50 p+p)

total £9) SPECTRUM KEYBOARD OVERLAYS @ £2.60 (35p p+p total \$2.95) 5 ROLLS ZX PRINTER PAPER @ \$1.55 (95p p+p total \$12.50)

I enclose remittance in full Please bill my Access/Barclaycard/Visa/

Overseas orders please add 25% for additional MINANE ADDRESS

DEALERS: Phone 01-403 6644 for enquirie

John Lambert discovers how the latest add-ons work.

#### 6 UPDATE

We return to previous issues.

#### NEWS

Latest on OL delays and awards.

#### 8 MOTOROLA 68008

John Mellor investigates the chip which is at the heart of the OL.

ADVICE COLUMN

In this issue we begin a new service for all with queries about projects they have attempted or would like to attempt. Trevor Marchant will be writing his advice column based on your problems.

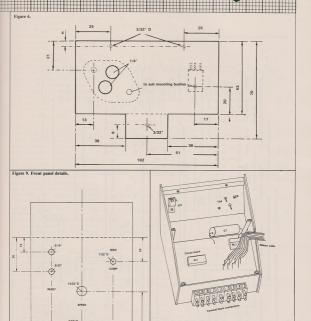

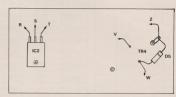

#### 18 DIGITISER

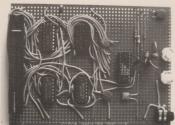

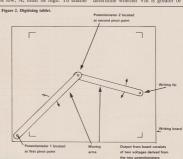

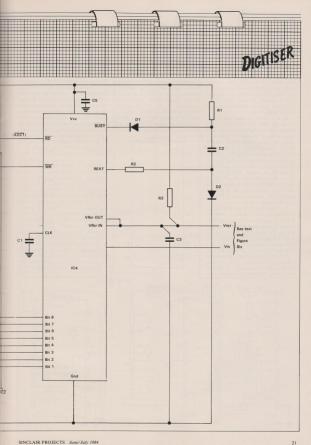

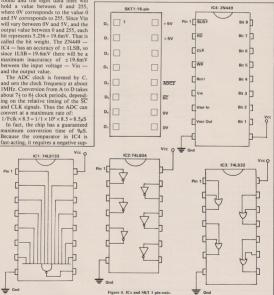

Corin Howitt explains how to build an input device for the Spectrum.

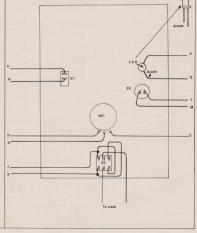

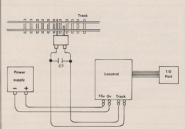

#### 26 LOCOTROL

Brian Lee allows you to control a railway system from your ZX-81 or Spectrum.

#### 36 SPECIAL OFFER

Save 25 percent on the cost of the new Kempston EPROM Centronics interface

#### 38 JOYSTICK

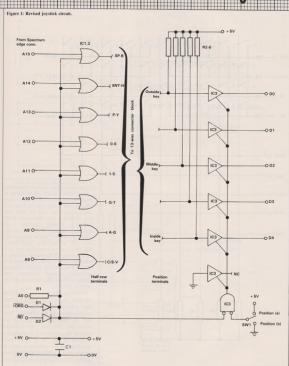

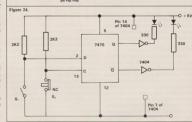

Corin Howitt returns to the project in the October/November issue which has caused readers some difficulties.

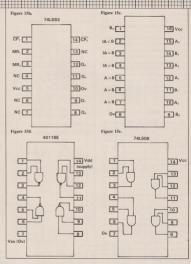

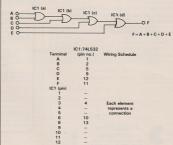

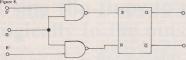

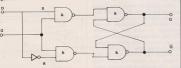

#### 42 DIGITAL ELECTRONICS

Joe Pritchard continues his guide to electronics by looking at logic devices.

Spotlight Magazine Distribution Ltd, 1 Benwell Road, Holloway, London N7, 01-607 6411.

ALL MANUFACTURERS of hardware like to keep people interested in their products by informing them what is to be launched. That long-awaited, low-cost mass storage device might just be around the corner; that high-powered new micro could be only weeks away from starting production.

Everyone has heard the claims, both outrageous and modest, and believed or rejected them depending on the amount of trust placed in the speaker. Given the record of Sinclair Research, there can have been few people who expected to receive QLs as soon as they were planned to go on sale at the end of February, but no-one expected to wait as long as they have before receiving a promise of seeing the results of their £400 investment.

It must be clear to everyone now that at the time of the launch in January, Sinclair did not have a QL. It had a box of assorted components and an idea of the kind of software it would like to go with it—but in between there was a vawning ean.

All those hundreds of people who paid £400 and placed their orders have taken a quantum leap in the dark. They would have been better-advised to keep their money in the bank earning interest which is now being earned by Sinclair Research. They have been promised a gift to sweeten their bitterness but Sinclair is able to pay for that with ease from the special account in which the money is being held

The company is trying to enter the professional market. It will have to show less naivety and more professionalism before it can hope to gain a toe-hold in an area where there is already a large number of companies with products to sell and the knowledge of how to go about it.

Meanwhile, if there is anyone who is still interested in what the QL is capable of doing, we will supply as much information about it as we can. In this issue John Mellor has been investigating the Motorola 68008 chip.

Following the new format we introduced in the last issue, we have another two hardware projects. For the Spectrum there is a digitiser which allows the direct input of graphics and for the ZX-81 and Spectrum, Brian Lee has built a model railway controller.

Continuing the development of the magazine we have started a problem-answering service. We have asked Trevor Marchant, a man with a wealth of knowledge of both the ZX-81 and the Spectrum, to write a regular column based on your queries. He is a busy man and cannot undertake to answer problems personally or on the telephone. He intends, however, to deal with areas which are of imnortance to all of your

Managing editor Nigel Clark Consultant editor David Buckley Managing production editor Harold Mayes MBE News writer John Lambert

Design Elaine Bishop Advertisement manager Holly Fleming Advertisement Executive Robert Marcus Editorial assistant Colette McDermott

Production assistant Dezi Epaminondou Assistant managing director Barry Hazel Managing director Terry Cartwright Chairman Richard Hease. Sinclair Projects is published bi-monthly by ECC Publications Ltd. It is in no way connected with Sinclair Research Ltd.

Telephone, all departments 01-339 325. If you would like to contribute to any of the Stockier Liver group of publications please send programs, arricles or ideas for hardware projects to Sinclair User and Projects, ECC Publications, 196-200 Bails Pond Road, London NI 4AQ, We pay 150 per 1,000 words for each article used.

© Convinited 1984 Sinclair Projects: ISSN 0564/4949, Printed and tweest by Cradley Print PLC. Warley. W. Midlands. Distributed by

# Disc system is twice as fast as Microdrive

OF THE MANY new disc systems which have appeared recently for the Spectrum, one of the first is the Viscount system from Interactive Instruments

Sin. Shugart drive with a hard-wired connecting cable. As there is no through connector on the interface, users who wish to add a printer interface will also ned some kind of extender connector which Interactive can also supply. The system will, at present, support only the one drive and uses a single-sided, single-density format. It is configured to give 10TK

of storage per disc.

The interface is housed in a very solid metal box; care should be taken when inserting the power lead, which plugs in the back, as it can short-out. Inside is a professionally-laid-out PCB. It is surprising that one of the standard disc operating chips is not used but instead a multitude of TTL chips. That is the reason for the non-standard storage canacity.

On power-up the contents of an 8K EPROM is loaded into the top 8K of memory; a number of variables taking another 110 bytes are loaded into the variables area and you are presented, on screen, with the message FIZ 83/540.1 OPERATING FIRMWARE, © 1983 Macronics Systems Limited.

The variable nd, used to format a new disc, is set to 64003 and used in the form RAND USR nd. For most of the commands f5 is first filled with the file name, plus any parameters. Those parameters are used to signify the auto-run line with Basic programs and the start, length and run addresses, in decimal, of CODE.

With arrays any number of DIMentioned arrays can be saved provided the total length per save is fewer than 2,816 bytes. Large arrays therefore must be split into parts and saved separately. The usual commands to obtain a directory, delete a file and duplicate a disc are also available.

The system is roughly twice as fast as a Microdrive, even allowing time to type the command, but it uses a great deal of RAM space. Business users could not use it for many of the usual business programs for that reason, although some specially-written software is becoming available.

Overall, the system works well and is your own programs. The system costs £245 inc. and is available from the Spectrum chain of shops or direct from the manufacturer, Interactive Instruments Ltd, Unit 6, Pilot House, King Street, Lejecster.

### Interface DOS now uses only 1K

THE DISC interface from Technology Research, reviewed in the last issue of Sinclair Projects, has been upgraded. The main changes are that you can now SAVE the variables by preceding the save name with #, that when auto-running the program does a OOTO I rather than RUN, and that the DOS uses only the upper 1K of the DOS uses only the upper 1K of old interface; and old interface can buy an upgrade.

The price of the new interface is the same as the old one, £85 plus VAT, and it can be obtained from Technology Research Ltd, 356 Westmount Road, London SE9 1NW. Tel: 01-856

#### Pen has positional error

AMONG Add-On Electronics Hardware is a light pen for the Spectrum. Included in the software provided with the pen are 16 routines to allow you to draw pictures.

The light pen has two parts. The pen contains a BPW 148 photo-rasister with one leg cut off. The intersister with one leg cut off. The interface box, into which the pen plugged, takes its power from the Spectrum power lead and has another lead to the Spectrum power socket. Vet another lead plugs into the Associate After the software has loaded. The pen works by timing the plugs spot of light on the TV from the start of the scan to where it is detected.

The interface amplifies the signal and uses the EAR socket as a port.

With a light pen the timing is allimportant, as a small time difference leads to a large positional error. This pen has a random positional error of up to 2in. which makes it almost impossible to use.

It was used on Sony Trinitron and Fidelity TVs but may work correctly with other sets.

At £30 the pen costs £10 more than others on the market. It can be obtained from Add-Ons Electronics, Units 2, 3 & 4, Shire Hill Industrial Estate, Saffron Walden, Essex CB11 3AO.

### Getting 16K on tap

FROM Camel Products, well-known for its EPROM products for the ZX-81, is the new ROM SP, an EPROMto-Spectrum loader. The unit can hold either one or two 2764s or one 27128, giving nearly 16K on tap. The unit is housed in a custom-

Light rifle is accurate up to 6ft.

A NEW IDEA on an old theme is the Stack Light Rifle from Stack Computer Services. It is a four-part sniper's rifle supplied with three games tapes, High Noon, Grouse Shoot and Shooting Gallery for the 48K Spectrum. Other versions of the Rifle are available for the Commodore 64 and Vic-20.

The main pistol is attached, via 12ft. of cable, to a dead-ended ZX-81-size edge connector which plugs into the rear user port of the Spectrum. To the pistol can be fitted a barrel, stock and telescopic sight.

The rifle works like some light pens in that it detects the flying spot of light on the TV screen. A photodiode in the pistol barrel picks up the spot and the software, when the trigger is designed ABS case and has a flexible connector to the back of the Spectrum; there is also an extender card on the back of the unit. On the top is a LED to show when a program is being transferred and a pushbutton switch. Inside the unit are two chips,

pulled, finds the X/Y position. It does so accurately from up to about 6ft. away. Overall the rifle is well-made and

Overall the rifle is well-made and the games highlight the kind of uses to which it can be put. At the time of writing other games are being written a few discrete components and two sockets for the EPROMs. Three Minicon pins are used to hard-link the unit to transfer on either power-up or by pressing the pushbutton. Another three are used to select the type of EPROM.

Users with an Issue 1 Spectrum may experience difficulties if the unit is set to transfer on power-up. That is because that issue is slow to set up initially.

No difficulties were found if the unit is set to work via the push-button or on any other issue Spectrums.

The unit provides a welcome addition to the Camel range of products and is designed to work alongside its PROMER-SP, a Spectrum EPROM blower, which has a program to optimise space on the EPROM which can be used for Basic CODE and DATA.

The ROM SP costs £29.95, as does the PROMER-SP, both plus VAT. EPROM erasers are also available from £18.95 plus VAT, all inclusive of p&p. Camel Products is at 1 Milton Road, Cambridge CB4 1UY. Tel: 0223-314814.

to use the rifle. The Stack Light Rifle costs £29.95 inc. VAT with the three games and can be obtained either direct from the manufacturer, Stack Computer Services Ltd, 290-298 Derby Road, Merseyside L20 8LN or local retailers.

# Tricky simulations of joystick actions

THE TRICKSTICK from East London Robotics could best be described as a joystick simulator. It is a 7inlong black plastic cylinder with six touch-sensitive pads which simulate the usual four joystick positions plus two fire buttons.

It is supplied with its own interface and a software trainer tape. The interface mimics the Kempston joystick standard and can therefore be used with many existing programs. In addition, it is possible to use up to eight Tricksticks at once and have proportional movement, selected by pins on top of the interface.

The touch pads are drawing pins which use the capacitance of your body to effect a voltage level. That is amplified by circuitry in the stick and is gated with a Spectrum supplied reference voltage. The relevant bit of the data byte is therefore set, or not, accordingly. Once set, the bit will revert to 0, the rate of change of the bit will depend of the capacitance, i.e.,

is proportional to the proximity of your finger to the drawing pin. The overall sensitivity can be changed by a small variable resistor at the top of the stick.

When using more than one Trickstick, the pins on top of the interface decide at which address the stick will sit; A5 and A6 are held low and A8 to A15 denote the address, all the other address lipse beine held high

With no moving parts, the Trickstick should last a long time and, as it is complete with interface, is reasonably-priced at only £34.50. It is available, by mail order, from East London Robotics Ltd, Gate 11, Royal Albert Docks, London E11.

#### Professional finishing

KELAN is producing a prototyping kit which can be used with the ZX-81, Spectrum or Jupiter Ace. The kit, part No HB/2090, will give a professional finish to any project and can be used for many of the designs in Sinclair Projects

In each kit is a prototype PCB with space for 12 16-pin ICs, 10 in comfort, and a Veroboard-style scratchpad. There is also a Spectrum-style 28-way edge connector which can be cut down for use on other machines, an extender card and a 9-pin D-type Atari-style PCB mounting socket. A case, similar to that used by Cambridge Computing for its joystick interface is provided.

Costing only £9.50 inc., the kit is very good value. For further information, Kelan (Hobbyboard), North Works, Hookstone Park, Harrogate, North Yorkshire HG2 7BU. Tel: 0423 838472

### UPDATE

FEBRUARY/MARCH Letters, page 12, line seven of M Farnsworth's letter should read '7620 has "p)" " should be'.

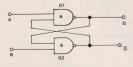

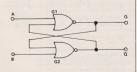

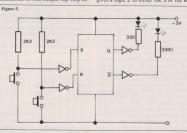

Digital electronics page [4, col. 2, line 11—7, is pronounced "A bat", of as'; col. 3, line 29—' remember that 0' as'; col. 3, line 29—' remember that 0' is 11:'; page 15 figure five—the & should not be in the NOT gate; col. 2, line 4 "A—A"; col. 3, line 29—' the function D.E. If the theorem is'; page [6, col. 1, line 29—"A,B = C; col. 1, line 30—"A,B = A B; page 17, col. 3, line 36—(A,B) = (A+B); col. 3, line 36—(A,B) = (A+B); page 17, col. 3, line 36—(A,B) = (A+B); page 17, col. 3, line 36—(A,B) = (A+B); page 18, col. 2, line 5 "(S,G=(A,B)+(A+B)); page 18, col. 2, line 5 "(S,G=(A,B)+(A+B)); que 18, col. 2, line 5 "(S,G=(A,B)+(A,B)); que 18, col. 2, line 5 "(S,G=(A,B)+(A,B)); que 18, col. 2, line 5 "(S,G=(A,B)+(A,B)); que 19, col. 2, line 5 "(S,G=(A,B)+(B,B)); que 19, line 5 "(S,G=(A,B)+(B,B)); qu

Automatic re-start, page 22, figure three—The NOR gate is joined to 5v

and IC1b; capacitor C3 should be labelled  $470\mu\mathrm{F}$ ; page 24, figure four—at the top end of the capacitor C1 there should be '+'.

Sound Board; page 38, figure two—the capacitor at the top left of the figure should be labelled C2 and lop, the variable resistor to the right of that is VRI; the capacitor further to the right is CI, beneath that C3 should be labelled 330p, R4 is 470g, and R5 is 470R. Page 39, figure two the right of the right of the two that the right of the right of the CI and to the left of that is socket SKI; page 40, program 5, line 180— POKE 16516, B.

RAM re-set; page 42, figure seven column headings are 'A13, Q2, A13,

A13'; page 43, figure eight-hatching in column A13 should be in the top half with the bottom half being clear; page 45, figure three-the arrow at the top near line 25 should be labelled RESIN, on IC9 the fourth pin from the top on the right-hand side is connected to 5v and the connections near 4K7 are shown incorrectly. The connection on line 18 should be with capacitor C4 and there should be a connection between lines 19 and 26; page 46, figure six-to the right of resistor R1 should read 'A15 to pin 6 of '138'; page 46, figure four-labelled warm-reset circuit diagram, on IC9a the top is connected to +5v and the bottom of resistor R3 is connected to 0v.

### **Deliveries delayed**

SINCLAIR RESEARCH is hoping its problems with the delivery of the OL will be over soon. At the time of

#### Pigment printout

COLOUR PRINTING can now be done from the Spectrum. Euroelectronics of Cheltenham has produced Copy Four software which allows users of the company's ZX Lprint Centronics and RS232 interface to print in four colours on the MCP 40 or Tandy CGP 115 printers.

Costing £5.50, the cassette is in two versions, machine code for the Mk111 model and Basic for earlier models or other interfaces, such as those built by Kempston and Tasman.

going to press the company was promising that all delivery dates which have been given to customers would be met.

It refused, however, to indicate the dates for the first deliveries. Journalists were able to test production models at the company offices in London from April 17.

Sinclair Projects was told by a reader who placed an order at the end of February that he has been given a delivery date of the end of July. Sinclair said in January that production would begin at the end of February and soon afterwards orders should take no more than 28 days to satisfy.

A spokeswoman said that a gift was being considered for people who had paid by cheque and whose money

Spectrum keyboard

**ENABLES ACCURATE DATA ENTRY**

Simple modification for ZX-81

was in a holding account.

#### Peripheral of the Year

THE MICRONET system is receiving increasing acclaim. Following its success in the RITA awards at the WHICH COMPUTER? Show, the Prism VTX 5000 modem was named as Peripheral of the Year in the British Microcomputing Awards.

It was selected because of its ability to put low-cost telecommunications before micro users. It won narrowly from the Epsom RX80 printer and the Torch disc pack.

The Spectrum and BBC B shared the What Micro? Home Microcomputer Award, with most of the other hardware titles going to the ACT Apricot.

The VTX 5000 allows Spectrum owners to access viewdata services, including Micromet 800 and Prestel.

#### new MASTERPLUG ELIMINATES ALL THAT UNTIDY WIRING

\* Neon on/off indication.

outlet socket

- \*1.5 metre lead with mains plug supplied. \*Enables 4 appliances to be connected safely, compactly and economically into one mains

- \*Complete with four special easy to connect plugs-no more to buy

- \*Safe-complies with BS 5733 and Electrical Equipment Safety Regulations 1975 (amend-

- \*Easily fitted to any surface with screws

£8.49 +50p p&p each

\*46 keys plus full length space bar. \*6 user keys—wired for special functions of

your choice. \* Ergonomically designed for ease of use \*Key identity legends protected by transparent plastic keycaps-will ner \*Reliable professional keyboard used by in-

\*Keys incorporate cantilevered contacts isolated from key return dynamics, to ensure contact pressure is independent of key oper-

\* Keyboard designed to be used independantly of housing if requi Keyboard with

Housing .. .£59.95 +£2 p&p Keyboard only ......£39.95 +£1 p&p

#### ALPHACOM 32 SPECTRUM COMPATIBLE PRINTER

Full interfacing to Spectrum/ZX-81

\*Quiet, maintenance free

\* High speed operation \*Uses low cost easily available paper

\*Comes complete with user manual, one roll

of paper, and power supply unit. \*Self test facility

\* Automatic feed

low cost

\*Uses standard Sinclair print commands: COPY, LLIST and LPRINT OUT,

\* Paper available from us @ £12.00 including p&p (10 rolls, each 25 metres long).

£59.95 +0.4

PLEASE SUPPLY (state which computer)

......Description .....

.....Price (inc p&p £ .....

Send cheques/POs now to: H & K Supplies, 27 Inglewood, Woking, Surrey, GU21 3HX.

\* Contacts gold alloy inlay

# Getting to the heart of the Quantum Leap

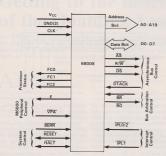

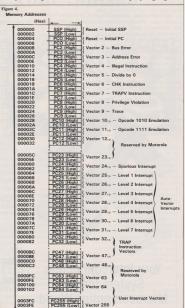

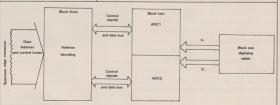

The 68008 chip from Motorola is one of the main reasons for the low cost of the QL. John Mellor discovers its capabilities and how it is organised with a 16-bit microprocessor and an eight-bit data bus while retaining the 32-bit architecture

T THE HEART of the Sinclair QL computer are two processors. One is the 68008 microprocessor chip and the other the 8048 single-chip micro-controller.

The 68008 is a member of the 68000 microprocessor family. The micro-processors are designed and manufactured by Motorola and second-sourced by Mostek Corp, Hitachi Ltd, Philips, Rockwell Int, Signetics and Thomson EFCIS. Second-sourced means that those manufactured by Motorola and Second-sourced means that those manufactured and those manufactured means that the means the means that the means the means

turers also manufacture them by agreement with the chip designer Motorola.

It is important for Sinclair or any microcomputer manufacturer that it can obtain components from more than one source to minimise the chances of industrial action or the policy decisions of the suppliers af-

fecting production.

The 68008 is a 16-bit microprocessor with an 8-bit data bus. The 8-bit data means that it is cheaper and

REGISTER

Table 1

DBCC

| Mnemonic Description |                               |

|----------------------|-------------------------------|

| ADBC                 | Add Decimal with Extend       |

| ADD                  | Add                           |

| AND                  | Logical And                   |

| ASL                  | Arithmetic Shift Left         |

| ASR                  | Arithmetic Shift Right        |

| BCC                  | Branch Conditionally          |

| BCHG                 | Bit Test and Change           |

| BCLR                 | Bit Test and Clear            |

| BRA                  | Branch Always                 |

| BSET                 | Bit Test and Set              |

| BSR                  | Branch to Subroutine          |

| BTST                 | Bit Test                      |

| CHIC                 | Check Register Against Bounds |

| CLR                  | Clear Operand                 |

| CMP                  | Compare                       |

Test Condition Decrement and

Description

Signed Divide Unsigned Divide

| EOR                                    | Exclusive Or                                                                            |

|----------------------------------------|-----------------------------------------------------------------------------------------|

| EXG                                    | Exchange Registers                                                                      |

| EXT                                    | Sign Extend                                                                             |

| JMP                                    | Jump                                                                                    |

| JSR                                    | Jump to Subroutine                                                                      |

| LEA                                    | Load Effective Address                                                                  |

| LINK                                   | Link Stack                                                                              |

| LSL                                    | Logical Shift Left                                                                      |

| LSR                                    | Logical Shift Right                                                                     |

| MOVE<br>MOVEM<br>MOVEP<br>MULS<br>MULU | Move Multiple Registers<br>Move Peripheral Data<br>Signed Multiply<br>Unsigned Multiply |

| NBCD                                   | Negate Decimal with Extend                                                              |

| NEG                                    | Negate                                                                                  |

| NOP                                    | No Operation                                                                            |

| NOT                                    | One's Complement                                                                        |

|                                        |                                                                                         |

| Mnemonic | Description                  |

|----------|------------------------------|

| PEA      | Push Effective Address       |

| RESET    | Reset External devices       |

| ROL      | Rotate Left without Extend   |

| ROR      | Rotate Right without Extend  |

| ROXL     | Rotate Left with Extend      |

| ROXR     | Rotate Right with Extend     |

| RTE      | Return from Exception        |

| RTR      | Return and Restore           |

| RTS      | Return from Subroutine       |

| SBCD     | Subtract Decimal with Extend |

| SCC      | Set Conditional              |

| STOP     | Stop                         |

| SUB      | Subtract                     |

| SWAP     | Swap Data Register Halves    |

| TAS      | Test and Set Operand         |

| TRAP     | Trap                         |

| TRAPV    | Trap on Overflow             |

| TST      | Test                         |

#### DDOCDAMMING MODEL

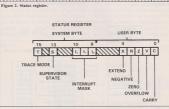

Figure 1. 68008 register.

| 31                | 16   15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8 7    | 0                   |    |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------|----|

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1      | D0                  |    |

|                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1      | D1                  |    |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -      | D2                  |    |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | - 1    | D3 EIGHT            |    |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        | DATA<br>D4 REGISTER | 00 |

| -                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1      | D5                  | 10 |

| -                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        | D6                  |    |

| -                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1      | - D7                |    |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                     |    |

| 31                | 16-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | belief | 0                   |    |

| Treat 17          | Marin State State of the State |        | AO                  |    |

| gog sidskow       | o place two of south                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        | A1                  |    |

| SIRGIP COLUMN     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        | A2                  |    |

|                   | Personal Property lies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | A3 SEVEN<br>ADDRESS |    |

| - line            | THE REAL PROPERTY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        | A4 REGISTE          | RS |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        | A5                  |    |

| - he in the       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        | - A6                |    |

| 100               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                     |    |

| COLUMN TO SERVICE | USER STACK POIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TER    | A7 TWO ST           |    |

| SI                | UPERVISOR STACK F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | OINTER | A7 POINTER          | S  |

| 31                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                     |    |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        | 1 PROGRA            | м  |

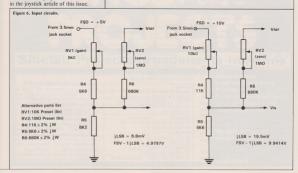

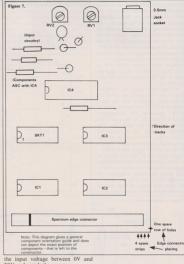

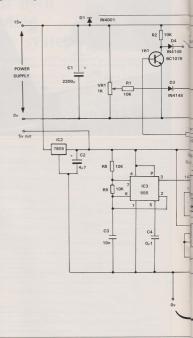

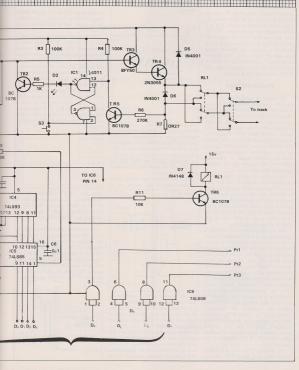

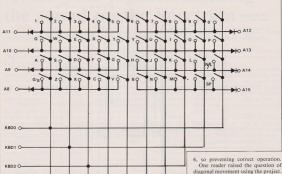

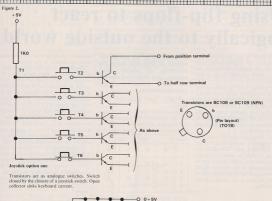

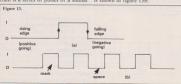

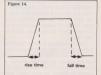

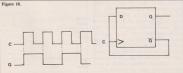

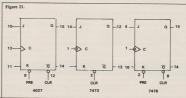

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        | COUNTE              |    |